本次代写是集成电路的一个assignment

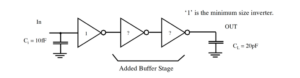

1. [CMOS Inverter Power Dissipation] This is a follow-up problem for homework 3 problem 3. Using the

same circuits (as shown in the figure) and the results obtained from the previous sub-questions,

determine a closed form expression for the power consumption in the circuit. Consider only gate

capacitances in your analysis. What is the dynamic power consumption for a supply voltage of 2.5𝑉𝑉 and

an activity factor of 1?

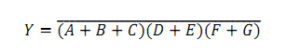

2. [Static Behavior of Complementary CMOS] The AND-OR-INVERT (AOI) and OR-AND-INVERT (OAI)

gates are two types of widely used standard cells in the digital IC design. The OAI322 gate means

logically the gate is composed of three OR gates, one AND gate, and one INV gate (inverter). The

number of the inputs of the OR gates are 3, 2, 2 respectively. The outputs of the of the OR gates will

drive the AND gate, and the output of the AND gate will drive the INV gate. The function of the OAI322

gate can be expressed as:

(a) Use the complementary CMOS to implement the above OAI322 gate. Derive the expressions for

both pull-down and pull-up networks, and draw the schematic of the digital circuit.

(b) Suppose the size of all the NMOS is (W/L)𝑁𝑁𝑁𝑁𝑁𝑁𝑁𝑁 = 2 and the size of all the PMOS is

pull-down and pull-up networks under the best and worst cases respectively.

Hint: The best case means that under this input pattern, the output resistance of the network is

the lowest. The output resistance is the equivalent resistance of the network seen from the

output 𝑌𝑌 to the ground (if pull-down network) or the power supply (if pull-up network), which is

the equivalent resistance of the network’s 𝑅𝑅𝑃𝑃𝑁𝑁 when the network is on.