本次美国代写是一个集成电路的assignment

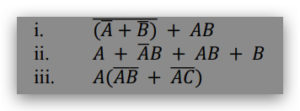

Question 1.

Implement the following logic expressions in full static CMOS using the minimum number of

logic gates:

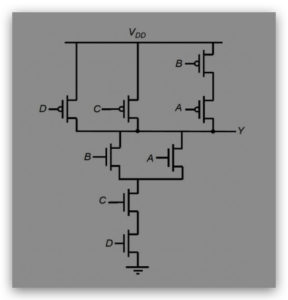

Question 2.

Given , find a complementary CMOS circuit that implements X. Select

device sizes so the output resistance identical to an inverter with an NMOS W/L = 2 and PMOS

W/L = 6. What input pattern(s) would result in the worst and best equivalent pull up or pull

down resistances?

Question 3.

The figure below shows a circuit that implements a logic function

Answer the following questions about the circuit:

a) Derive the logic function of the transistor network. Size NMOS and PMOS devices so

the output resistance is the same as an inverter dimensions: NMOS W/L = 4 and

PMOS W/L = 8.

b) Find the input patterns that give the worst case tpHL and tpLH. State the initial input

patterns clearly and specify which input(s) must transition in order to achieve this

maximum propagation delay. Consider the effect of the capacitances at the internal

nodes.

c) You are given the following: P(A=1)=0.5, P(B=1)=0.2, P(C=1)=0.3 and P(D=1)=1,

Find the power dissipated by the network. Use the assumption VDD=2.5V,

Cout=30fF and fclk=250MHz.

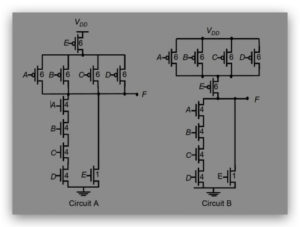

Question 4.

Answer the following question based on circuits A and B given above

A. Do the two circuits above implement the same logic functions? If yes, what is that logic

function? If no, derive a Boolean expression for both circuits.

B. Do these two circuits always have identical output resistances?

C. Do these two circuits always have identical rise and fall times? Why or why not?